반도체 패권전쟁에서 최근 Hot한 뉴스는 역시 삼성전자의 3nm GAA의 발표와 TSMC와의 수율전쟁의 뉴스입니다.

여기에 Intel도 미래의 칩기술을 선점하기 위해 ASML사의 HighNA장비의 첫 구매자와 동시에 Intel4 Chip의 Roadmap을 발표을 했고, 관련된 많은 정보들은 기술에 생소한 일반인들에게도 이제는 이해가 될만큼 이 3개의 거대한 Chip maker회사들의 수율경쟁은 반도체기술업계에서는 주요 관심사로 뉴스에 많이 나오고 있습니다.

ASML사의 EUV공정은 ArF공정과는 다른 13.5nm EUV파장광원을 다루기 위한 EUV Mask 즉 광원의 반사도를 기반으로 하는 기술이라 여러가지 기술적인 장벽이 있는데, 특히 Tech Node가 줄어들면서 수율과 관련된 Defect과의 싸움은 반도체제조공정에서는 영원한 숙제중의 하나입니다. 이 기술을 이해하기 위해서는 EUV및 관련된 주변의 기술과 Chip maker고객의 수율전쟁을 큰 시각에서 보면 재미있는 주제가 될것 같습니다.

먼저 EUV노광장비에 사용되는 칩디자인의 패터닝이 그려진 EUV Mask(레티클이라고도 함)는 아래와 같이 얇은 루테늄 층으로 덮인 실리콘(Si)과 몰리브덴(Mo)의 40~50개의 교대 층으로 형성되어 250~350nm 두께의 다층 스택이 있고, 이 스택에서 Mo와 Si의 다층은 입사광을 반사하는 반면 탄탈륨-붕소-질산염(TaBN)으로 만들어진 흡수체는 반사를 차단합니다.

아래의 개요도는 일반적인 구조의 모습입니다.아래 그림의 absorber(흡수체)는 일반적으로 충분한 양의 EUV빛을 흡수하도록 설계된 약 60-70nm 두께입니다. 이 두께는 13.5nm 노광 파장에 비해 크기때문에 결과적으로 특정 입사각(기존 EUV 리소그래피에서 약 6° 중심)에서 마스크에 부딪히면서 흡수를 하게 됩니다.

따라서 현재 EUV장비이후의 차세대 High NA EUV(NA:개구부,낮은 DOF)장비의 렌즈구성설계와 광원의 입사각이 마스크의 Absober의 두께와 연관되어 영향을 미치며 또 다른 기술적 숙제(쉐도잉 이펙트문제등)가 되는것입니다. EUV노광기술의 진화에 따라 Mask의 Material도 바뀌고 부가적인 기술들(Resist두께등등)이 바뀌는 이유이기도 합니다.

EUV용 Mask의 제조공정 또한 이전의 ArF광원에서 다루었던 Mask자체와 다르기 때문에 제조공정도 아래과 같이 Multilayer포함 새로운 물질들이 증착이 되는 구조라서, 이에 패터닝시 수율과 연관된 다양한 Defect들이 존재를 하게 됩니다. 따라서 Defectivity의 Control이 더욱 중요하게 되지요.

위에서 설명한 이러한 EUV Mask의 외부Defect을 보호하는 EUV Pellic(펠리클)이 필요한데, 즉 이런 EUV마스크는 매우 중요하고 직접적으로 Chip의 수율에 영향을 주기 때문에 보호하는 것이 중요합니다.물론 매우 비싸기도 합니다. 그런 보호의 용도와 위에서 기술한 다양한 문제들을 방지하기 위해 펠리클이 필요합니다.간단히 생각해보면 Defect등이 마스크에 떨어지지 않도록 보호막같은 역할입니다.(아래 그림). 이 페리클은 에너지가 높은 13.5nm EUV 파장에서 매우 강하게 흡수하며, 멤브레인(막)은 90% 투과율에 도달하기 위해 극도로 얇아야 합니다.

현재 이 EUV페리클 기술이 양산적용단계까지 완성이 되면서 수율향상을 위한 일부의 칩 제조공정에 일부 적용이 이미 되고 있습니다. 아주 일부 또는 부분적으로 적용이 되고 있습니다. 이 페리클 또한 매우 비싸고 소모성의 부품이라 사실 수율관점에서 Defect의 관리만 된다면 안쓰는것이 공정비용절감과 투과율확보에서는 가장 바람직하다고 할수 있습니다.

페리클은 실제 HVM((high-volume manufacturing)사에서 어떻게 적용이 되고 있을까?

최근 인텔의 HighNA 방식의 차세대 최신 노광기를 수천억에 구입하는 뉴스를 접하셨을것입니다.(기사검색참조) 인텔의 경우는 단일 다이 레티클을 사용하여 대형 칩을 개발하는 경향이 있기 때문에 EUV 펠리클을 선택을 해야 할것 같습니다. 예를 들어 단일 다이 레티클(패터닝된 Mask를 레티클이라고 말함)의 단 하나의 파티클 생성으로 발생하는 수율저하가 100%라고 생각한다면 동일한 시나리오에서 2-다이 레티클에서는 50% 적은 수율저하로 가정을 할수 있습니다.

따라서 펠리클의 적용은 당연히 큰 다이 크기가 중요하며 동일한 웨이퍼상에서 작은 Die칩보다는 크고 비싸고 수율에 더 민감한 칩에 필요합니다.(Cost의 관점). 인텔과 같은 Big die나 고가의 CPU/GPU등의 칩Maker입장에서는 삼성이나 마이크론등에서 제조하는 Dram/Flash이상으로 필요할 것 입니다. Logic Chip이 메모리보다 페리클을 더 사용해야 하는 이유이기도 합니다. 인텔이 High NA와 같이 페리클적용에 더 관심이 있고 적용의지가 강한 이유이기도 합니다.

인텔의 이야기로 넘어가 볼까요? 인텔4(INTEL4)는 인텔이 EUV공정으로 가는 가장 중요한 기술시점?

아래 2022년 6월에 기술포럼에 칩디자인의 전문 기고자가 쓴 흥미로운 글을 보게 되었습니다.. Intel4 칩의 페리클적용에 관련된 내용입니다.

Careful EUV Lithography Adoption for Intel 4

(Intel 4를 위한 신중한 EUV 리소그래피 채택)

One of the biggest changes in Intel 4 is the introduction of EUV lithography tools for select layers. Samsung, TSMC, and Intel all target different applications and are pursuing different approaches to EUV. Generally, Intel tends to be fairly conservative about lithography. EUV was always considered for the 10nm family, but it was not ready for volume manufacturing in the right time frame, approximately 2017, particularly for high-performance logic applications. Instead, the company used self-aligned quad-patterning (SAQP) for metal layers and vias requiring 40nm pitch and below.

One factor in play is that while Intel has its own EUV mask-making subsidiary, the company is relying on the industry (i.e., ASML and now Mitsui) for pellicles that protect the masks from persistent defects caused by particles

한 가지 요인은 Intel에 자체 EUV 마스크 제조회사(Maskshop)이 있지만 파티클에 기인한 지속적인 결함으로부터 마스크를 보호하는 펠리클에 (즉, ASML 및 현재 Mitsui공급)에 의존하고 있다는 것입니다.

. The pellicle does not perfectly transmit EUV illumination and will reduce the intensity delivered to the wafer by twice the transmissivity, reducing tool throughput and increasing cost.

For layers with dense patterns such as the metal interconnects, a pellicle is mandatory – the risk of a particle hitting an active portion of the pattern is simply too high. However, some sparser layers e.g., contacts and vias may be feasible to print without a pellicle.

메탈 인터커넥트와 같은 Dense한 패턴이 있는 레이어의 경우 펠리클이 필수입니다. 파티클이 패턴의 Active Area에 부딪힐 위험이 너무 높습니다. 그러나, Contact 및 Via와 같은 일부 여유가 있는 Layer는 펠리클 없이 노광을 하는 것이 가능할 수 있습니다. ASML 펠리클은 꽤 오랫동안 개발 중이지만 2021년 초에 겨우 90%의 투과율에 도달했으며 시간이 지남에 따라 계속 개선될 것입니다.

위에서 언급한 EUV공정을 인텔Node4에 적용한 사례로 아래 Intel4 공정에 EUV Pellicle이 적용되었다고 추측을 할수 있을것 같습니다. 또한 설명했던 Defect(결점)제거가 MC(Metal contact)이나 Via에 아주 중요하다는 사실입니다.

아래는 Intel4의 Metal CS(Cross Section) 구조와 적용된 내용의 사례입니다. 칩의 EM역시 EUV적용후 성능이 향상되었음을 보여주고 있습니다.

인텔4 칩의 공개된 정보를 더 찾아보았습니다. Gate pitch 50nm, fin pitch 30nm, minimum metal pitch 30nm, 16Metal Layer에 Cobalt 대신에 저항및 EM 특성이 개선된 Cu공정을 사용한 FINFET공정인데 위의 그림의 하단쪽 Metal Interconnect쪽에 EUV공정을 사용함을 설명을 했습니다. 이 설명으로 보면 MC(Metal interconnect)중에서도 상단의 널널한(Non-Dense 패턴)이 아닌 SoC칩의 하단쪽 Dense쪽의 Critical한 MC위주로 적용이 되었을것 같습니다.

인텔의 로드맵은 EUV공정과 페리클의 사용?

인텔의 Node별 위의 발표내용을 보면 EUV공정의 흥미로운 적용시점도 엿볼수 있습니다. Intel4에서 EUV를 전면 적용을 했고 Intel3에서 EUV사용을 늘린다는 내용이죠.

최고의 선두업체 TSMC 상황은? 페리클을 자체개발?

The ASML pellicle has been under development for quite some time, but only reached 90% transmissivity in early 2021 and will continue to improve over time.In contrast, TSMC developed its own pellicle in 2019, which enabled ramping EUV into volume with Apple’s A14 on the 5nm node.

대조적으로, TSMC는 2019년에 자체 펠리클을 개발하여 5nm 노드에서 Apple의 A14와 함께 EUV를 볼륨으로 확대할 수 있었습니다.

TSMC는의 4~5nm급에서 이미 EUV공정으로 생산을 하고 있으며, 페리클을 자체개발 생산을 하고 동시에 ASML사의 페리클도 사용하는것으로 알려져 있습니다.

TSMC의 페리클 개발의 루머와 내용에 대해서는 여러차례 업계에서 소문이 돌고 있지만, TSMC와 연관된 대만의 뉴스를 검색을 해보니 어느 구인광고에 페리클개발자 구인이 나오면서 우연히 포스팅이 노출이된것이 대만에서 뉴스거리가 되었습니다. 극도의 비밀유지가 되고 있으나 전반적인 내용으로는 자체 개발된 기술이 높은 수준으로 업계에서는 판단되며 적용도 하고 있다고 추측을 하고 있습니다.

삼성을 제치고 애플이라는 큰 고객을 잡고 잘나가는 TSMC의 2022년 1분기 실적이 발표가 되었는데 눈여겨 볼 부분이 5nm의 매출비중입니다. 이 5nm급이 APPLE의 A14 칩의 매출로 위에서 언급한 EUV공정으로 생산되는 제품입니다. A14는 애플이 모바일 SoC(System on a Chip)인 애플 A14 바이오닉이라는 칩인데 트랜지스터 수는 118억개로, 우리가 사용하는 아이패드 에어 (4세대) 아이폰12, 아이폰 12 미니, 아이폰 12 프로, 아이폰 12 프로맥스등이 이 칩셋을 사용한 제품입니다. 2020년 N5 양산의 시작과 함께 애플의 5nm물량을 전량 수주하면서 급격한 매출의 증대를 아래 두 그래프로 보여주고 있습니다.

필자는 TSMC와 삼성전자의 공개된 투자자 자료와 검색을 해보면서, 기업투자의 Investor에 대한 투명성이 극명하게 차이가 나는 부분을 느낄수 있었습니다. 외국인 투자자들이 한국투자를 꺼리는 이유중의 하나도 투자자들에게 투명한 기업정보 공개를 하는것인데. 특히 사업방향에 대해서는 삼성전자의 공개하는 정보와는 사뭇 대조적으로 보입니다.

TSMC는 단순한 기술적으로 앞선 일류기업뿐만 아니라, 전세계 투자자들에 대한 정보공개의 투명성에 대한 기업철학도 삼성전자보다 앞서고 있다는 개인적인 생각이 들기도 합니다.

잠시 패너닝측면으로 다시 보면 N5(5nm)칩이 TSMC에서 EUV공정적용을 하면 기술적으로 앞에서 설명했듯이 Mask갯수가 줄고, 생산단가(결국 노광부터 에치까지)연결되는 DP,QP등 2~3중이상의 더블패터닝공정이 EUV한공정으로 해결이 가능하게 됩니다. 간단히 설명하면 그림5장을 노가다와 비용을 들어 그리는 그림을 1장의 정교한 그림으로 찍어 낸다는 이야기지요. 패터닝뿐만 아니라 다중공정의 모든공정에 연관된 Risk들도 같이 줄어들게 되며. 제조비용이 줄어드는것은 당연하게 따라가게 됩니다.

반도체의 Chip설계는 결국 세대가 바뀌면서 성능이 좋아지는것이고.. Chip은 작게 선폭을 줄이면서 소비전력,Speed,성능향상이 목적인데, 위에서 주제로 다루는 페리클의 적용과 Chip maker의 사용량이 연관되어 설명이 가능하지 않을까 합니다. 결국 미세선폭부분의 중요한 공정만큼 Defect을 줄이기 위해 점차적으로 페리클의 사용량이 더 늘어날게 될것입니다.

TSMC에 대해 조금 더 이야기를 해보자면 N5(5nm칩이라고 합시다)의 모든 성능이 위의 그림과 같이 향상이 됨을 설명합니다.이전 7nm대비 소비 전력이 같을 경우 속도가 15% 향상되고, 속도가 같다면 전력 사용량이 30% 줄어들었고, 또 로직 회로의 밀도는 모바일 버전에서 최대 1.84배 늘어나며, SRAM 셀의 밀도도 1.35배 오르게 되었습니다.. SRAM 밀도가 1.35배인데 논리 회로가 1.8배인 이유는 공정 기술과 회로 설계의 최적화인 DTCO(Design-Technology Co-Optimization)로 로직 셀의 크기를 줄이기 때문이라고 설명을 하고 있습니다.

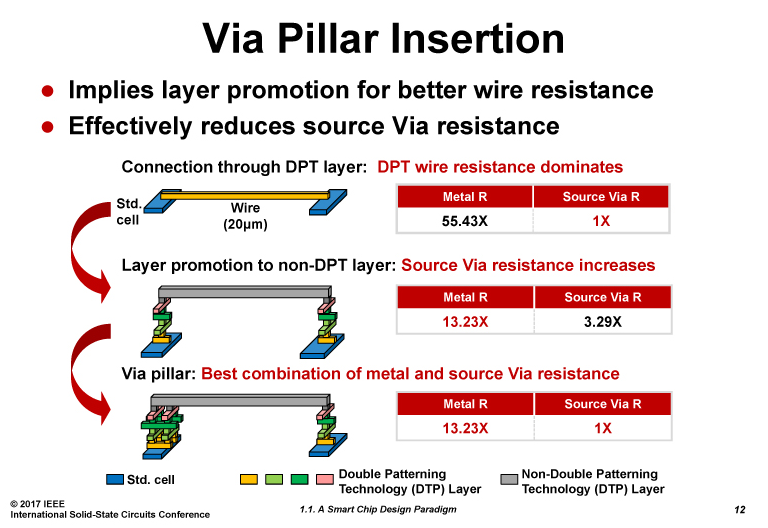

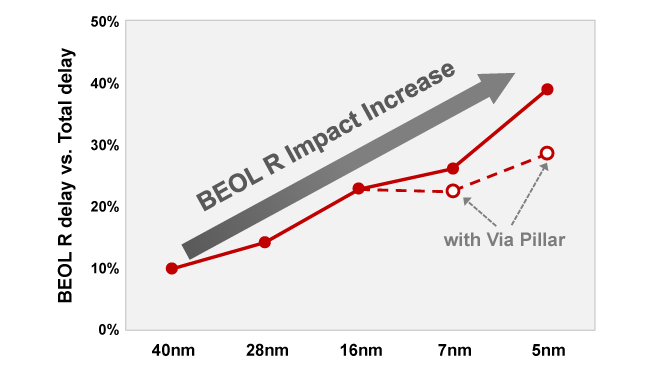

이제 언급했던 Metal Interconnect의 EUV Pellicle공정 도입의 이유가 설명이 되는데, TSMC는 N5에서 특히 MC(Metal Contact)의 Via Pillar Insertion를 광범위하게 도입이 되었습니다. N7에선 시험적인 도입었으나, 5nm부터는 본격적으로 사용을 했습니다. 현재 첨단 공정은 배선층의 하부(하층) 부분의 배선이 가늘어 저항이 크고. 따라서 트랜지스터보다는 배선(Metal Connect)에서 생기는 지연이 더 큰 영향을 준다. Via Pillars를 사용하면 배선의 저항(Via resistance)이 줄어드는 효과가 있습니다. 아래 MC의 구조(그림)를 보면 DPT(Double Patterning)의 구조중 하부Layer쪽의 저항이 커지는 미세선폭쪽의 Metal connect적층구조를 Cell부분에 이중으로 Contact하는 공정으로 Via resistance를 줄인다는 설명이 나옵니다.

이 구조는 반도체의 Structure와 Etch/Photo/Overlay등을 이해하는 전문가들은 쉽게 이해를 하는 내용입니다.

제 생각에는 Logic Device에서 미세선폭의 싸움은 BEOL의 저저항 싸움이며, 여기 Metal Interconnect와 EUV의 적용필요성 그리고 제조수율향상을 위한 Pellicle사용도 결국 필요하리라 보여집니다.

최근 2022년 반도체 기사중의 가장 큰 뉴스는 아래 삼성전자의 4nm공정의 수율(반도체웨이퍼한장에서 불량없이 뽑아내는 Chip의 확률)문제였지요?.(아래 기사 참고).

Samsung Foundry’s 4nm yield for Snapdragon 8 Gen 1 chips reportedly very low

https://www.sammobile.com/news/samsung-foundry-4nm-yield-snapdragon-8-gen-1-chips-very-low/

Samsung Foundry’s 4nm yield for Snapdragon 8 Gen 1 chips reportedly very low

While Samsung is the world's biggest memory chip maker, it is a distant second in contract logic chip manufacturing. The ...

www.sammobile.com

During its 54th annual shareholders’ meeting, the South Korean firm revealed that more advanced semiconductor process nodes (like 4nm and 5nm) are pretty complex, and it will take time to improve yields. It is being reported that Samsung Foundry’s yields for 4nm Snapdragon 8 Gen 1 chips are very low at just 35%. If this information is correct, it is a matter of concern for the company.

The MediaTek Dimensity 9000 chipset, which is fabricated on TSMC’s 4nm node, is reportedly more power-efficient than the Exynos 2200 and the Snapdragon 8 Gen 1 that are made on Samsung’s 4nm process.

그렇다면 수율문제는 위에서 언급한 Chip의 성능(물론설계는 고객사인 Qualcomm)이겠지만, TSMC와 삼성의 차이점에 어떤 기술이 차이가 생겼는지에 대한 궁금증이 생기게 되었습니다.

수율은 반도체 제조회사에 이익과 직결되는 가장 중요하고 극비적인 데이타입니다. 즉 회사의 수익성과 연결되는 문제이지요. 수율을 0.1%향상을 위해 반도체의 거대한 공장의 모든 엔지니어와 연구자들이 일을 하는 목표이기도 합니다.

그러나 수율의 이유는 단순히 하나의 원인으로 보기에는 로직반도체의 제조 공정의 복잡성과 연계성으로 단정을 짓기는 어렵습니다.. 그러나 여러 정보로 추정을 해보면 위의 TSMC가 애플이라는 거대한 고객을 잡은 큰 이유는 BEOL기술(MC의 저항을 잡는 기술)의 차이가 아닐까요?

애플의 기술력은 혁신이고 앞서간다.

위의 그림에서 애플의 막강한 Mac용 칩은 TSMC의 최첨단 5nm 노드에서 제조됩니다.

애플제품과 안드로이드 기반의 제품을 비교해보면 가장 차이점은 AP차이인데, 왜 애플칩이 뛰어날까요? 이 부분은 칩설계의 이해가 필요한데, 아래의 자료에 어느정도의 이해를 할수 있었습니다. 저전력설계와 성능의 분배에서 SoC칩설계 자체에서 차이가 납니다. 이 이상의 칩설계의 기술적인 내용은 여러가지 기사와 정보로 따로 확인하면 이해를 하실수 있습니다. 결론은 애플은 엑스노스나 스냅드래곤과 차별화된 칩 설계의 기술력이 있습니다.

아래에서 같은 Arm Core를 사용하지만 애플칩은 스냅드래곤와 성능에서 높은 차이를 볼수 있습니다.

여기에 더하여 5nm M1칩에 이어붙힌 막강한 칩(M1 Ultra)가 등장합니다.

이 Die(칩의 조각단위)를 붙이는 인터포져기술은 인텔의 EMIB기술로 보고 있는데. EMIB는 (임베디드 멀티 다이 인터커넥트 브리지, Embedded Multi-die Interconnect Bridge) 기술로 여러 칩을 모두 연결하는 획기적인 기술로 인텔이 발표한 기술입니다. 이쪽은 BEOL(패키징)기술이라 다음에 자세히 다루도록 하곘습니다. 아래 영상과 자료를 참고하시기 바랍니다.

인텔의 패키징 기술에 영상을 Link합니다.

애플칩이 어려운 이유는 위의 FEOL(전공정)과 BEOL(후공정)의 기술이 필요합니다. TSMC가 다른 차별점은 EUV를 이용한 전공정의 기술노하우도 있지만, 고객위주의 Foundary서비스를 하면서 BEOL(패키징)관련 기술력이 앞서기 때문입니다., TSMC는 애플의 5nm칩을 2022년 초 전량 주문을 받은 이유입니다.

EUV와 페리클의 적용에 대한 주제를 다루었지만, EUV공정의 단순한 이해는 최신 Tech node의 Chip의 생산에 필요한 포토공정의 일부분일 뿐입니다. 전세개 big chip maker의 보이지 않는 기술과 설계의 싸움에 따라 그 칩을 생산하는 삼성전자,인텔,TSMC의 치열한 기술경쟁의 진화가 EUV에 달려있지만, 미래에는(미래라 함은 3nm이하의 2nm)에서는 FEOL에서는 안정된 수율확보를 위해 결국 포토공정에서 페리클적용이 보다 늘어날것입니다. 여기의 전제조건은 BEOL(패키징)기술도 같이 따라와야 한다는것입니다. 웨이퍼위의 Die의 수율과 Interposer기술을 이용한 정교한 패키징기술이 같이 필요한 이유이기 때문입니다. TSMC가 마켓을 잡고 가는 이유가 아닐까요?

'반도체' 카테고리의 다른 글

| 반도체의 EUV HighNA 시대가 무어의 법칙을 깬다. (0) | 2023.08.05 |

|---|---|

| 대한민국 반도체의 역사의 시작과 삼성전자 반도체 기흥사업장 (0) | 2023.08.04 |

| 실리콘카바이드 웨이퍼 SIC반도체 특성 4H-SIC를 쓰는 이유 (0) | 2022.06.04 |

| ASML은 왜 Berliner Glas라는 독일회사를 인수를 했을까? (0) | 2022.03.22 |

| 중국 반도체 장비회사의 현황 (0) | 2021.12.28 |