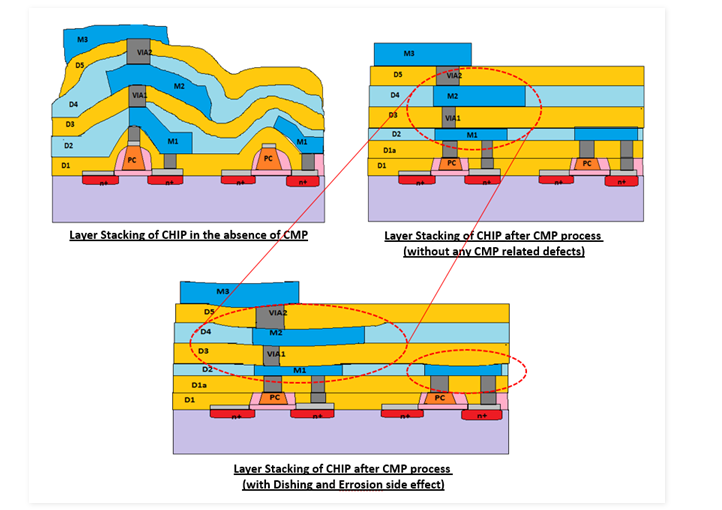

구리 디싱(Copper dishing)과 SiO2 침식(SiO2 erosion)은 바람직하지 않습니다. 이는 구리 라인의 최종 두께를 줄이고, 표면의 평탄도를 저하시켜 여러 금속 레벨을 추가할 때 복잡성을 초래하기 때문입니다. 현재 정의를 찾고 있다면 조금 기다려야 할 수도 있습니다. 지금은 아래 그림을 통해 이 두 가지 현상의 시각적 정의를 도울 수 있습니다.

구리 디싱(Copper Dishing)

- 정의: 구리 디싱은 화학 기계적 연마(CMP) 과정 중 구리의 과도한 제거로 인해 금속 라인이 움푹 들어가는 현상입니다.

- 영향: 디싱은 구리 라인의 두께를 줄이고, 금속 표면의 평탄도를 손상시켜 다층 금속 배선 공정에서 문제를 일으킬 수 있습니다.

SiO2 침식(SiO2 Erosion)

- 정의: SiO2 침식은 화학 기계적 연마(CMP) 과정 중 절연막(SiO2)이 과도하게 제거되는 현상입니다.

- 영향: 침식은 절연층의 두께를 감소시키고, 표면의 평탄도를 손상시켜 다층 배선 공정에서의 평탄화를 어렵게 만듭니다.

그림 설명

- 구리 디싱: 그림에서는 금속 라인이 움푹 들어간 형태로 표현됩니다. 이는 연마 과정에서 구리가 과도하게 제거된 결과입니다.

- SiO2 침식: 그림에서는 절연층이 얇아지거나 불규칙하게 제거된 형태로 나타납니다. 이는 연마 과정에서 SiO2가 과도하게 제거된 결과입니다.

이 두 가지 현상은 다층 금속 배선 공정에서 중요한 문제로 작용하므로, 이를 최소화하기 위한 공정 개선이 필요합니다. Hitachi와 AMAT와 같은 회사들이 이러한 문제를 해결하기 위해 하드웨어 개선을 도입하고 있는 이유입니다.

이제 두 가지 질문이 있을 수 있습니다: 왜 그리고 어떻게 이러한 문제들(침식과 디싱)이 여러 금속 층을 추가할 때 평탄도 문제를 일으키는가? CMP 없이도 평탄도가 좋지 않았다는 것을 이전에 언급한 바 있습니다. CMP는 이를 제거하기 위한 것이지만, 다시 평탄도 문제를 이야기하고 있습니다. 그렇다면 두 종류의 평탄도 문제의 차이는 무엇일까요? 이 글에서 두 가지 질문에 답해 보겠습니다.

첫 번째 포인트는 다음 그림과 그 설명을 통해 이해할 수 있습니다.

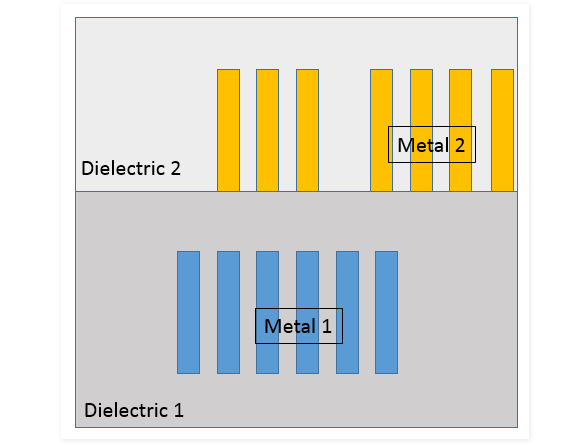

2D 이상적인 VIEW:

기본적으로 여기서는 문제가 없을 경우를 설명하려고 합니다.

- Metal1의 모든 판이 동일한 기준 높이(즉, 웨이퍼의 "0"/"제로" 높이에 대한 높이)에서 시작합니다. 이들은 동일 평면상에 있습니다.

- Metal1의 모든 판 두께가 동일합니다.

- Dielectric1의 두께는 디자인 전반에 걸쳐 동일해야 합니다.

- Metal2의 모든 판이 동일한 기준 높이(즉, 웨이퍼의 "0"/"제로" 높이에 대한 높이)에서 시작합니다. 이들은 동일 평면상에 있습니다.

- Metal2의 모든 판 두께가 동일합니다.

- Dielectric2의 두께는 디자인 전반에 걸쳐 동일해야 합니다.

- Dielectric2의 시작 지점은 Dielectric1 바로 위에 있으며 직선으로 이어집니다.

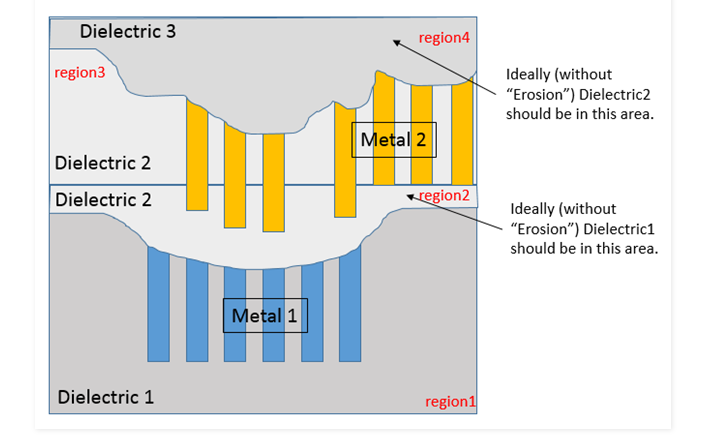

CMP로 인한 변화: 2D VIEW

CMP이후에는 금속 층과 절연층의 비균일성(불규칙성)이 생기고 높이와 두께의 변동이 발생합니다.

- Metal 1의 시작 높이는 동일합니다(이 아래는 모두 이상적이라고 가정했기 때문입니다).

- CMP의 부작용으로 발생한 디싱 때문에 Metal 1의 두께가 변했습니다.

- CMP의 부작용으로 발생한 침식 때문에 Dielectric1의 두께도 변했습니다.

- 금속 판이 있는 부분에서 더 많은 영향을 받고, 금속 판에서 멀어질수록 덜 영향을 받습니다.

- CMP 공정이 Metal1과 Dielectric1에 완료된 후에 Dielectric2를 증착하기 때문에 Dielectric2의 시작 높이는 Metal1과 Dielectric1의 최상부에 맞춰집니다.

- 아래 그림에서, Region2가 원래는 Dielectric1을 위한 영역이었지만 디싱과 침식 이후에는 Dielectric2의 일부가 되었습니다.

- 이제 이러한 표면에 Metal2를 증착할 때, Metal2의 시작 높이는 자동으로 변합니다(침식의 영향을 받은 Dielectric1의 최상부에 따라 달라지기 때문입니다).

- Metal2와 Dielectric2 구조에 대해 CMP를 하면 다시 평탄도가 왜곡되고 디싱과 침식이 다시 발생합니다.

- 원래 Dielectric2에 할당된 Region4가 이제 Dielectric3의 일부가 됩니다.

요약하면:

- M1에서 비균일한 구리와 절연 손실이 M2 및 더 높은 금속 레벨에서 손실을 악화시킵니다.

- CMP의 영향은 누적됩니다.

- 다중 레벨 효과는 초점 심도(DOF), 식각, 궁극적으로 수율에 영향을 미칩니다.

위 그림에서의 불규칙성은 이해를 돕기 위해 확대된 것이지만, 실제로는 CMP를 하지 않을 때 발생하는 불규칙성보다 훨씬 더 나은 상태입니다.

CMP의 영향을 완화할 수 있는 몇 가지 권장 솔루션이 있습니다. 예를 들어, 더미 필링(dummy filling)과 넓은 폭의 인터커넥트에 기둥/구멍을 넣는 방법 등이 있습니다.

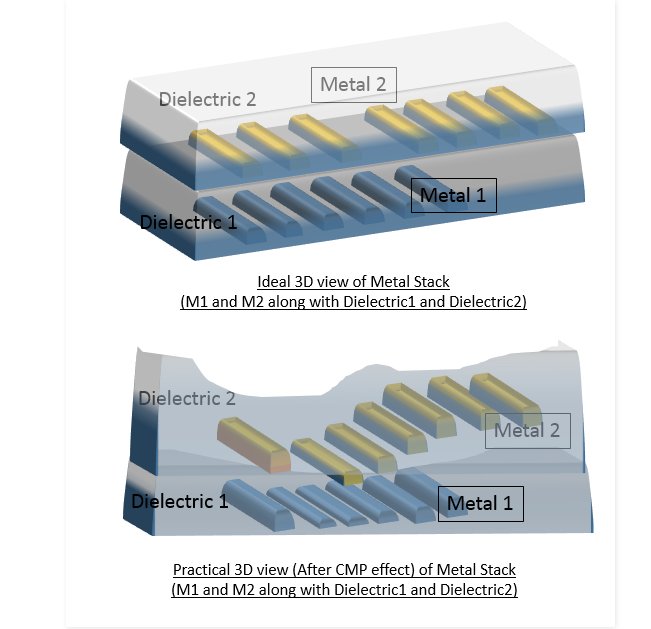

3D 뷰에서 동일한 내용을 설명을 한다면(아래 그림 참고)

이상적인 경우:

- 일정한 레벨링을 가진 동일한 금속 두께(시작 및 종료 지점에서)

- 웨이퍼 전체에 걸쳐 일정한 두께와 레벨링을 가진 절연층

그러나 CMP 후:

- 금속 층의 두께가 변합니다.

- 절연층의 레벨링이 변합니다(절연층 두께 변경).

- CMP 효과가 누적되어 다른 금속 및 절연층에 영향을 미칩니다.

즉 CMP로 인해 발생하는 불규칙성이 CMP 이전과 같지 않다는 주장을 정당화하기 위해 몇 가지 그림을 그렸습니다.

아래 그림들을 보면, 차이점과 CMP의 중요성을 쉽게 이해할 수 있을 것입니다. 가장 좋은 점은 몇 가지 최선의 방법과 다른 방법들을 통해 CMP의 부작용(침식 및 디싱 문제)을 최소화할 수 있는 방법이 있다는 것입니다.

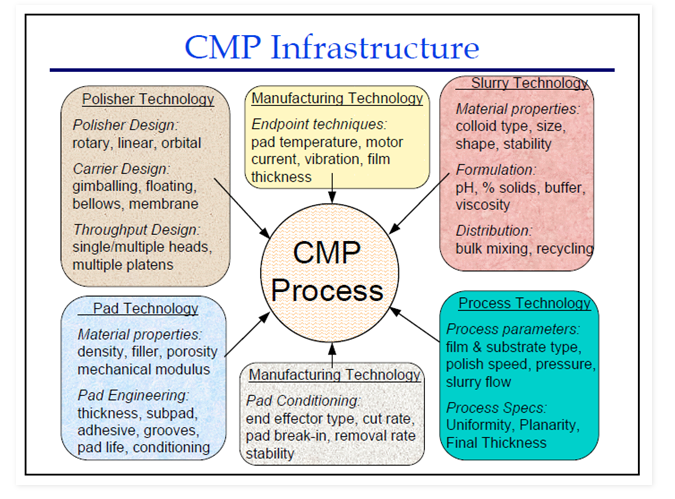

낮은 노드(90nm 이하)에서는 공정의 복잡성(다단계 효과)과 많은 매개변수(압력, 온도, 속도, 패드 재료, 슬러리 재료 등)에 의존하기 때문에 이러한 변동을 정확히 모델링하기가 매우 어렵습니다. CMP 공정의 복잡성은 다음 슬라이드를 통해 쉽게 이해할 수 있습니다

반도체 제조사 및 기타 협력사들은 다양한 물리적 효과(패드 속성, 압력, 연마 시간 등)와 화학적 효과(슬러리 종류, 제거율 등)를 고려하여 물리적 CMP(화학 기계적 연마) 공정을 시뮬레이션하는 접근 방식을 개발합니다.

*출처: VLSI

'반도체' 카테고리의 다른 글

| HighNA EUV 시대를 향한 포토레지스트 측정 및 결함 관리의 진전 (0) | 2024.08.01 |

|---|---|

| 삼성전자의 반도체칩렛과 AI용 패키징과 미래활용기술 (1) | 2024.08.01 |

| ASML사 HighNA도입에 따른 계측기술의 난제 (0) | 2024.07.31 |

| TSMC의 Packaging, Testing, Mask등 Foundry 2.0의 로드맵 발표 (0) | 2024.07.31 |

| 순간의 정책결정의 실수로 국민혈세 3000억을 날린 비운의 반도체공장 (2) | 2023.08.27 |