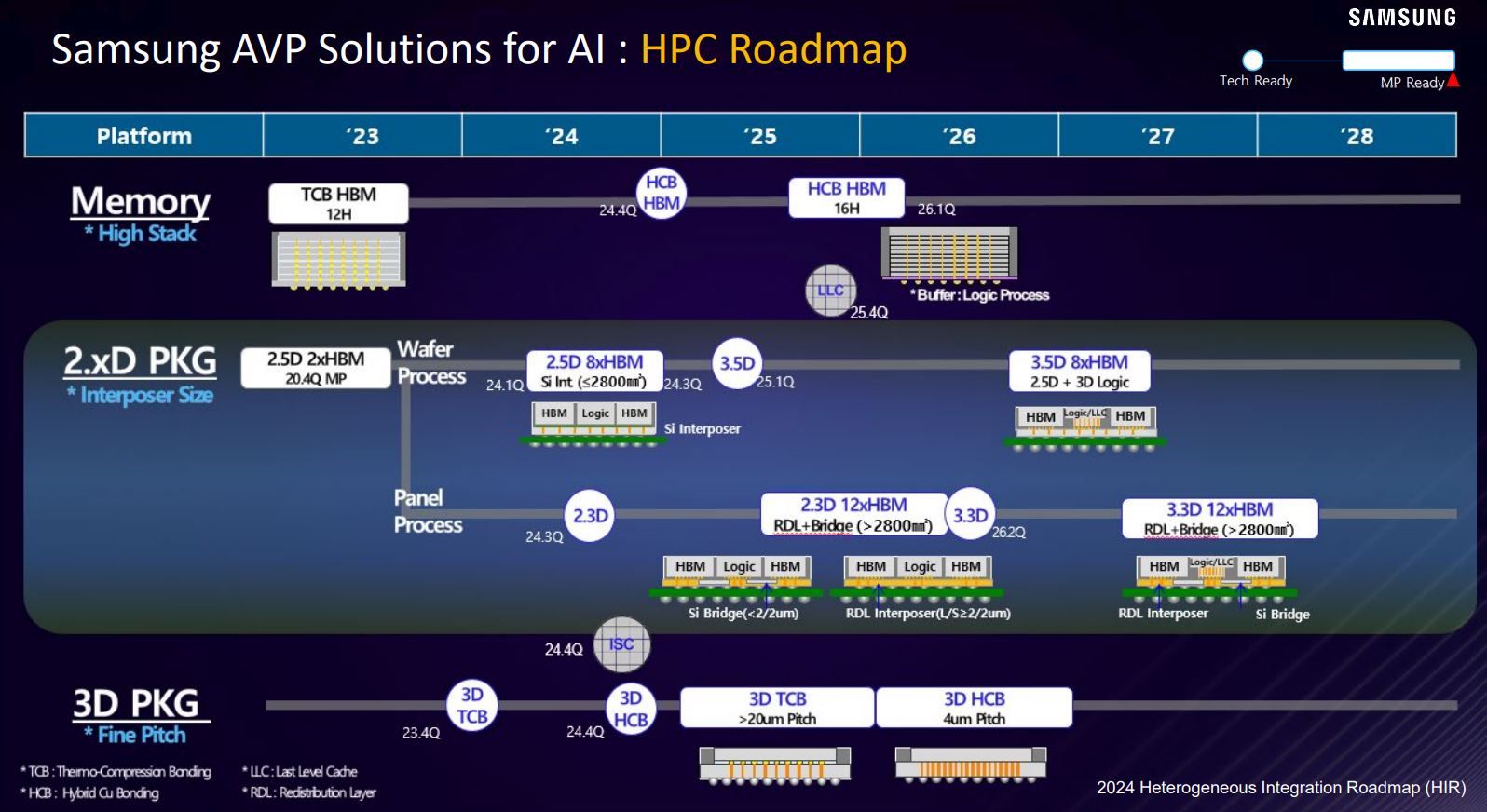

삼성의 AI용 AVP 솔루션을 살펴보면, 점점 더 많은 칩(칩렛)이 3D 또는 소위 3.5D 형태로 패키징되고, 오프칩 캐시 메모리가 내장되는 것을 볼 수 있습니다. 더 많은 컴퓨팅 파워가 작은 폼 팩터 "모듈"에 집적될수록 열 방출 및 관리가 어려워지는 것은 불가피합니다. 또한, 프로빙 없이 양품 다이를 확보하고 결함 없이 칩을 결합하여 높은 패키징 수율을 달성하는 것이 어려워집니다. 고가의 첨단 칩을 사용하기 때문에 패키징 공정에서 발생하는 결함 비용은 매우 높을 것으로 예상됩니다. 그렇다면 마이크로미터(um), 서브-마이크로미터, 심지어 10나노미터(nm) 수준의 디자인 규칙에서 묻힌 공정을 모니터링하기 위한 효과적인 3D 측정 기술은 무엇일까요? 결함 분석을 위한 결함 위치를 어떻게 식별할 수 있..