OPC(optical proximity correction)의 약자로 마스크 패턴을 웨이퍼에 비출 때, 미리 변형될 값을 계산하여, 이변형값을 보정하는 패턴을 의미한다.

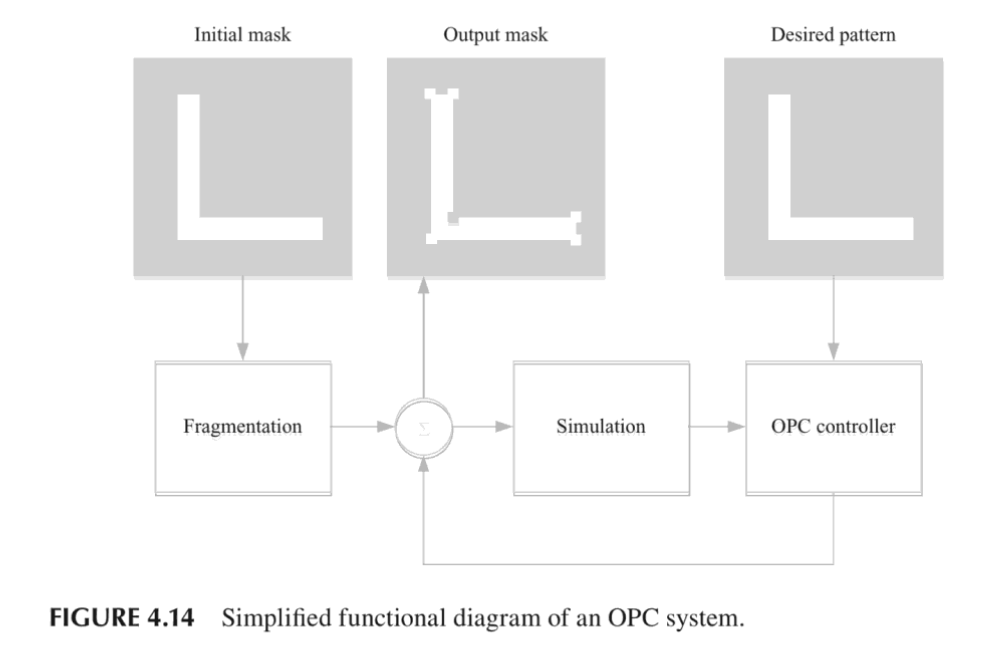

위의 Flow Diagram은 OPC Model에 의한 기본적 단계를 보여준다. 즉 Lithography Tool에서 Diffraction-Induced Limitation의 보정을 예상해준다.

Advanced OPC에서는 Mask상의 아주 작은 변화의 다각형(Tiny Perturbation Polygons)의 추가나 제거를 통해 웨이퍼의 특정위치상의 End Pattern의 개선된 결과를 만든다.

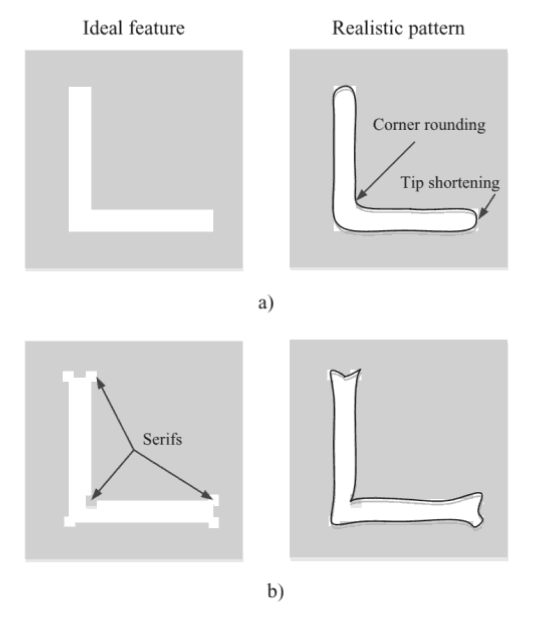

a) Solid white모양의 Mask Design과 검정색선은 OPC로 예상되는 패턴의 외곽선을 나타낸다.b) Serifs의 예로 디자인모양을 보정하는데 사용한다. 실제 웨이퍼상의 원하는 패턴에 가장 근접한 모양을 보여준다.

OPC의 이해를 위해서는 Wafer 패턴의 디자인 Tool EDA(Electronic Design Automation)SW의 설명이 필요하다.

EDA란 전자설계, 특히 반도체 제조 과정에서 회로 설계와 오류 검증을 미리 짜 놓은 컴퓨터 프로그램을 통해 처리·분석하는 작업을 말한다.

EDA툴이 제대로 보급되지 않았던 70년대까지만 해도 반도체 회로도를 만들기 위해서는 그림을 그리듯 엔지니어들이 블록(특정기능)별로 나눠 손으로 일일이 선과 선을 연결해야만 했고 최종 결과물에 대한 예측도 할 수 없었다.

그러나 70년대에 개발된 제1세대의 컴퓨터보조설계(CAD)가 도입되면서 레이아웃 설계가 자동화되고 80년대에 개발된 제2세대의 컴퓨터보조기술(CAE)은 논리 검증도 가능해졌다. EDA는 이 두 기술이 접목돼 90년대부터 본격화한 제3세대의 컴퓨터 종합 설계 환경으로 기능 설계는 물론 동작 결과치도 미리 분석해 볼 수 있어 개발기간을 획기적으로 단축시키고 오류도 줄일 수 있는 것이 특징이다.

현재 통용되고 있는 EDA툴은 크게 적용분야별로 필드프로그래머블게이트어레이(FPGA)·주문형반도체(ASIC)·인쇄회로기판(PCB)용이 있으며 특히 몇백만 게이트를 집적해야 하는 ASIC분야에는 전단계 로직설계 및 검증, 논리합성 툴과 후단계 레이아웃과 물리적 검증 툴 등으로 나뉜다.

주요 업체로는 시놉시스·케이던스·멘토그래픽스 등이 있으며 부문별로 특화된 기능을 개발한 중소 업체들도 상당수 있으나 대부분 선두 업체들과의 인수·합병을 통해 기술을 파는 것이 관례화돼 있다.

아래는 간단히 요약해서 보여주는 OPC System의 흐름이다. Output Mask의 Design과 원하는 Pattern의 Simulation을 복잡한 Modeling과 알고리즘을 통해 해석한다.

'반도체' 카테고리의 다른 글

| 왜 반도체제조에 Roughness와 Stochastics이 중요한가? (0) | 2021.09.01 |

|---|---|

| 반도체공정 웨이퍼 패터닝 기법 (0) | 2021.08.19 |

| RF Filter 시장 분석 및 Market Players (0) | 2021.08.13 |

| EUV(극자외선 Extreme ultraviolet)반도체 공정의 새로운 문제 (1) | 2021.08.12 |

| RF필터시장 및 와이솔(122990)분석 (0) | 2021.04.09 |