반도체 Dram의 이야기를 위한 글을 시작하려고 한다. 먼저 반도체 Dram의 첫 시작은 Isolation이다.

반도체에서 isolation은 트랜지스터와 같은 소자들 사이를 전기적으로 절연시키는 것을 의미합니다. 이는 소자 간의 전류 흐름을 방지하고, 의도하지 않은 회로 구성을 막기 위해 필요합니다. 일반적으로 유전체(dielectrics), 주로 산화물(oxide)을 사용하여 절연을 합니다. Isolation 방법에는 대표적으로 STI(Shallow Trench Isolation)가 있습니다.

즉 반도체 칩 내부에는 수많은 소자(트랜지스터, 다이오드, 저항 등)가 매우 좁은 공간에 밀집되어 있습니다. 이러한 소자들은 각자 독립적으로 작동해야 하며, 전기적으로 간섭 없이 자신만의 기능을 수행해야 합니다. 이를 위해 소자들을 전기적으로 격리하는 기술이 필수적입니다. 이를 자세히 설명해 드리겠습니다.

반도체 칩 내의 소자들은 각각 고유한 전압, 전류, 신호를 가지고 있습니다. 만약 소자 간에 전기적 격리가 이루어지지 않으면, 다음과 같은 문제가 발생할 수 있습니다:

- 전류 누설: 하나의 소자로부터 다른 소자로 전류가 누설되어, 의도하지 않은 신호 변조나 오류를 일으킬 수 있습니다.

- 신호 간섭: 서로 다른 소자 간의 신호가 섞이면서 데이터 전송 오류나 성능 저하가 발생할 수 있습니다.

- 고장 전파: 하나의 소자에서 발생한 전기적 고장이 다른 소자로 전파되어 칩 전체의 기능에 영향을 미칠 수 있습니다.

이러한 문제를 방지하기 위해, 각 소자를 독립적으로 격리하는 전기적 장벽이 필요합니다. 이것이 Isolation입니다.

Shallow Trench Isolation (STI, 얕은 트렌치 격리)는 반도체 소자 간의 전기적 간섭을 방지하기 위해 사용하는 중요한 기술 중 하나입니다. 이 기술은 특히 고집적 회로에서 많이 사용되며, 각 소자가 독립적으로 작동할 수 있도록 전기적으로 격리하는 역할을 합니다.

STI공정의 전기적 특성과 신뢰성에 대해 공부해 봅시다.

INWE(Inverse Narrow Width Effect, 역 협폭 효과)는 반도체 공정에서 채널 너비가 좁아질 때 발생하는 전기적 특성의 변화를 나타내는 현상입니다. 이 현상은 일반적인 **NWE(Narrow Width Effect, 협폭 효과)**와 반대되는 방향으로 나타나기 때문에 "Inverse"라는 용어가 붙었습니다.

Narrow Width Effect (NWE)

- 협폭 효과는 MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)에서 채널의 너비가 줄어들 때, 표면 전하의 분포와 변동 때문에 드레인 전류가 변하거나 문턱 전압이 높아지는 현상입니다. 즉, 채널이 좁아지면 문턱 전압이 증가하고, 트랜지스터의 성능이 저하될 수 있습니다.

Inverse Narrow Width Effect (INWE)

- 역 협폭 효과는 반대로, 채널 너비가 좁아질수록 문턱 전압이 감소하는 현상입니다. 이는 채널의 가장자리에서 전계가 더 강해지고, 그로 인해 표면 전하가 증가하면서 문턱 전압이 낮아지기 때문입니다. 이로 인해, 전류가 증가할 수 있습니다.

INWE는 NWE와는 다른 메커니즘으로 작용하며, 반도체 소자의 성능과 특성에 큰 영향을 미칠 수 있습니다. 공정에서 이 현상을 잘 이해하고 제어하는 것이 중요합니다.

Double Hump IV 특성은 반도체 소자의 전류-전압(IV) 특성 곡선에서 두 개의 피크 또는 험프(hump)가 나타나는 현상을 말합니다. 이 현상은 주로 MOSFET(Metal-Oxide-Semiconductor Field-Effect Transistor)과 같은 소자에서 관찰되며, 특정 공정 조건이나 소자 구조에서 발생할 수 있습니다.

Double Hump IV 특성의 원인

- 이중 게이트 구조 또는 변형된 채널 구조:

- 소자에 두 개의 게이트가 있거나, 이중 채널을 가지는 구조에서 서로 다른 두 채널이 각기 다른 문턱 전압을 가질 수 있습니다. 이로 인해 각각의 채널이 활성화되는 전압 범위가 달라 두 개의 험프가 나타날 수 있습니다.

- 불균일한 도핑 농도:

- 채널 내에서 도핑 농도가 불균일하거나, 트랜지스터의 게이트 산화막 두께가 다르게 형성된 경우, 서로 다른 영역에서 전계가 다르게 형성될 수 있습니다. 이로 인해 두 개의 다른 문턱 전압이 나타나고, IV 특성에서 두 개의 험프가 나타날 수 있습니다.

- Hot Carrier Injection (HCI) 및 소자 열화:

- Hot Carrier Injection에 의한 손상으로 인해 채널 영역의 일부가 다른 부분과 달리 문턱 전압의 변화가 발생할 수 있습니다. 이러한 소자의 열화 현상은 시간이 지남에 따라 Double Hump 현상을 더욱 두드러지게 만들 수 있습니다.

- 트랩(trap) 및 결함의 존재:

- 산화막이나 인터페이스에서 발생하는 트랩이나 결함이 트랜지스터의 특정 전압 구간에서 전류 흐름에 영향을 줄 수 있습니다. 이로 인해 IV 특성에서 비정상적인 두 개의 험프가 나타날 수 있습니다.

Double Hump IV 특성의 영향

Double Hump IV 특성은 소자의 성능 및 안정성에 부정적인 영향을 미칠 수 있습니다. 특히, 예측할 수 없는 동작이나 소자의 신뢰성 저하를 야기할 수 있으며, 이는 고속 또는 저전력 소자 설계에 있어서 중요한 문제로 작용할 수 있습니다. 이러한 특성을 완화하거나 제거하기 위해서는 소자의 제조 공정이나 설계에서 적절한 대책을 강구하는 것이 필요합니다.

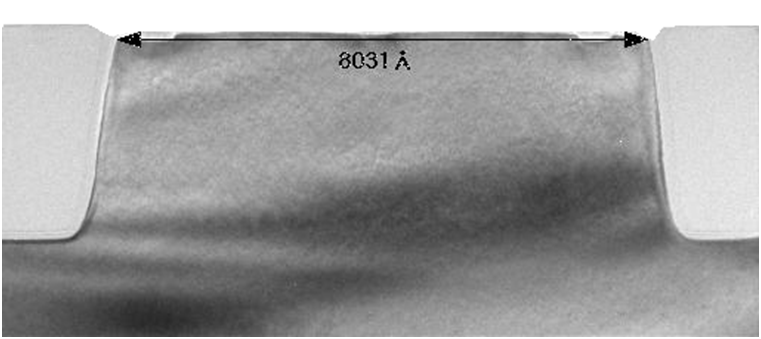

실제 STI를 통해 Active Pattern이 형성된 모습입니다.

'반도체' 카테고리의 다른 글

| 반도체 메모리 DRAM이야기 3편 (0) | 2024.08.12 |

|---|---|

| 반도체 메모리 DRAM이야기 2편 (0) | 2024.08.11 |

| TSMC 2024 기술동향과 로드맵소개,패키징포함 (1) | 2024.08.02 |

| 반도체 EUV미세공정에 따른 CD측정 도전과 Hitachi사GT2000의 혁신 (0) | 2024.08.01 |

| 어플라이드머티리얼즈사의 Centris Sym3 Y Magnum: EUV 패터닝과 식각 성능의 혁신적 향상 (0) | 2024.08.01 |