이번에는 Dram의 GATE형성과정입니다.

Gate Poly Oxide 공정은 DRAM 트랜지스터의 게이트 구조를 형성하는 핵심 공정입니다. 게이트 산화막 형성, 폴리실리콘 증착, 포토리소그래피, 에칭, 어닐링 등 일련의 공정을 통해 고성능의 게이트 전극이 만들어집니다. Gate Poly Oxidation 공정은 반도체 제조에서 중요한 단계로, 폴리실리콘 게이트 위에 얇은 산화막을 형성하는 과정을 말합니다. 이 산화막은 게이트 전극의 절연 및 보호 기능을 제공하고, 나중에 형성되는 Metal Gate 및 Dielectric Layer와의 계면 특성을 향상시키는 역할을 합니다.

Gate Hump 처리 공정은 트랜지스터 게이트의 물리적 또는 전기적 특성에서 발생할 수 있는 불균일성이나 결함을 보정하기 위한 기술을 말합니다. "Gate Hump" 현상은 주로 게이트의 중앙부가 불균일하게 돌출되거나, 전기적 특성이 다른 영역과 차이가 발생하는 문제를 일컫습니다. 이는 특히 초미세 공정에서 중요한 문제로, 소자의 신뢰성에 부정적인 영향을 미칠 수 있습니다.

Gate Hump 현상

- 폴리실리콘 증착 불균일: 폴리실리콘 증착 과정에서 두께가 일정하지 않거나, 증착 속도의 변화로 인해 게이트의 중앙부가 과도하게 두꺼워질 수 있습니다.

- 식각 공정의 문제: 식각 공정에서 균일한 식각이 이루어지지 않으면, 게이트 중앙부에 잔여물이 남아 돌출된 형태를 만들 수 있습니다.

- 열처리 공정: 열처리 과정에서의 열 분포 불균일이나 기계적 스트레스가 게이트 구조에 영향을 미쳐, 특정 부분이 비정상적으로 돌출될 수 있습니다.

- 게이트 산화막 형성 불균일: 산화막 형성 과정에서 불균일하게 성장하면 게이트 중앙부의 특성이 다른 영역과 달라질 수 있습니다.

Gate Hump 처리 공정은 반도체 제조에서 매우 중요한 단계로, 미세한 공정 변동으로 인한 게이트의 불균일성을 해결하는 기술입니다. 이 공정을 통해 트랜지스터의 신뢰성을 높이고, 소자의 전기적 특성을 최적화할 수 있습니다.

BPSG (Boron Phosphosilicate Glass) 공정은 반도체 제조에서 ILD1 (Interlayer Dielectric 1) 공정으로 사용되며, 주로 1차 금속 배선층 위에 절연층을 형성하는 데 활용됩니다. 이 공정은 특히 BPSG의 저융점 특성을 이용해 금속 배선 사이의 갭을 메우고 평탄화하는 데 유리합니다.

ILD1의 공정중 BPSG공정은 VOID문제가 발생합니다. 이것을 Control하는것이 중요합니다.

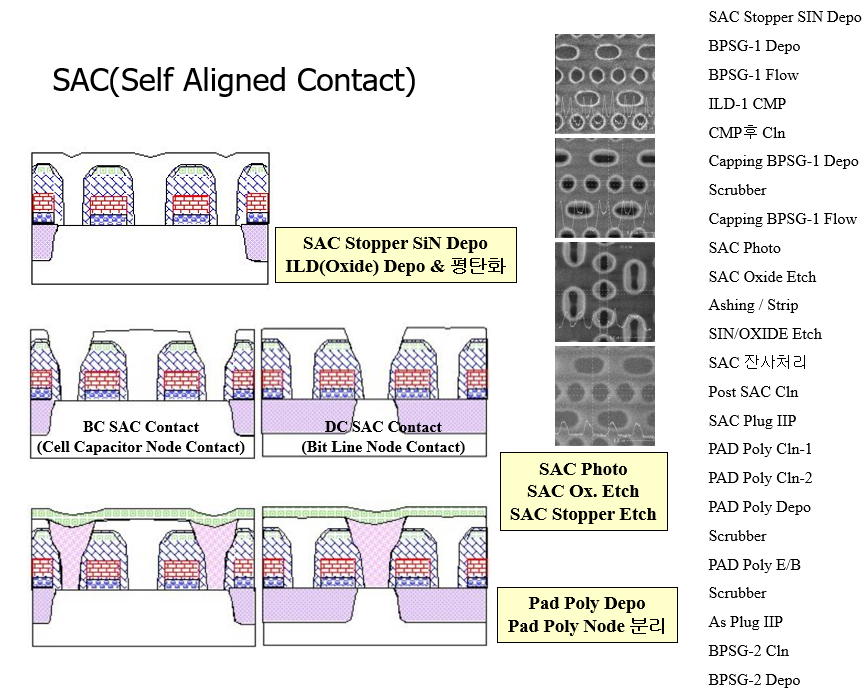

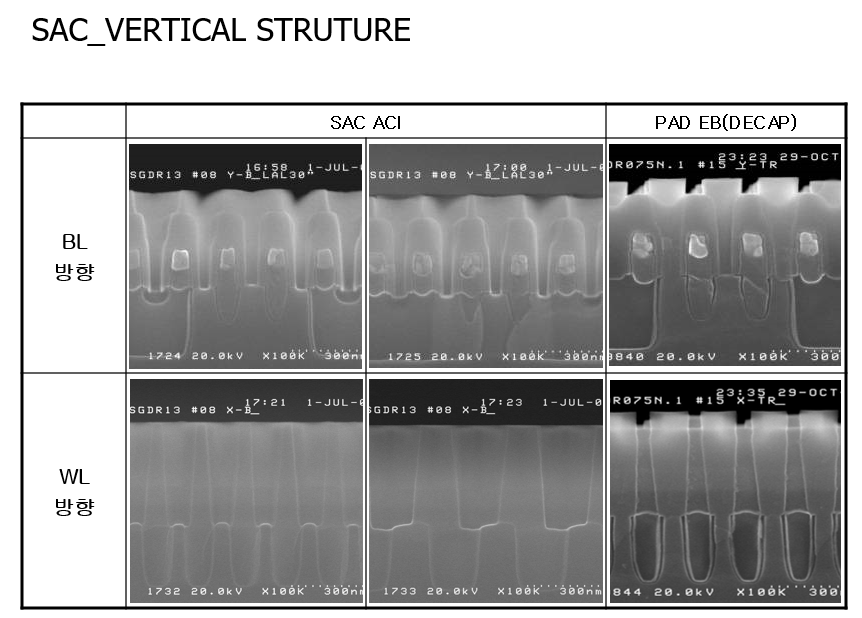

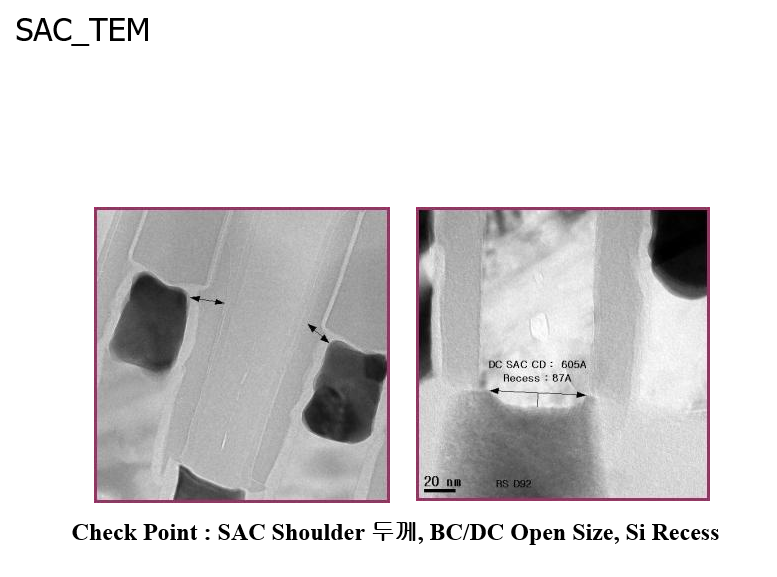

Self-Aligned Contact (SAC) 공정은 반도체 제조에서 소자 크기가 줄어들고 배선 밀도가 높아짐에 따라, **컨택 홀(Contact Hole)**을 형성하는 과정에서 발생할 수 있는 정렬 오차를 최소화하기 위해 사용되는 기술입니다. 이 공정은 주로 금속 배선과 활성 영역 사이의 접촉을 형성할 때, 정확한 위치에 컨택 홀을 형성하도록 돕습니다.

기술 노드가 축소되면서 배선과 게이트 전극, 소스/드레인 영역 사이의 거리가 줄어들었습니다. 이는 컨택 홀을 형성할 때 발생할 수 있는 정렬 오차로 인해 게이트 전극이나 인접한 배선과의 단락(Short) 문제가 발생할 가능성을 높입니다. SAC 공정은 이러한 단락 문제를 방지하고, 정렬 오차에 대한 공정을 견고하게 만들기 위해 개발되었습니다.

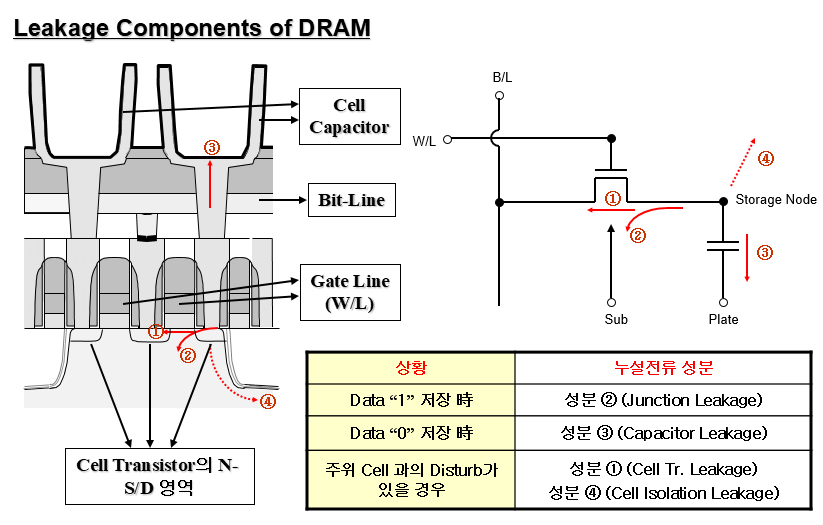

REFRESH란?

CELL에 DATA를 써놓고 일정시간이 지난 후에 DATA를 읽었을 때 내부 또는 외부의 영향에 의해 DATA의 일부분이 손실 되게 된다. 이러한 DATA의 손실은 DEVICE에 바로 영향을 주게 되어 DEVICE가 오 동작을 일으키게 된다.

이것은 쉽게 말하면 항아리에 물을 붓고 한참 시간이 지난 후에 항아리에 들어 있는 물을 보았을 때 물의 양이 자연적으로(항아리 자체의 결함, 햇빛,...등에 의해) 감소하는 것과 같은 이치이다.

따라서 이러한 data손실이 device에 영향을 주기 전에 다시 cell에 data를 써넣는 행위를 Refresh 해준다라고 말하고 각 cell에 대해 refresh할 때까지 걸리는 시간을 Refresh Time(TREF)이라 부른다.

Cell에 써넣는 data의 Refresh Time을 측정하는 방법에 따라 STATIC or DYNAMIC Refresh로 구분한다.

'반도체' 카테고리의 다른 글

| AI칩 nvidia TSMC의 CoWoS 구조 (3) | 2024.08.23 |

|---|---|

| 반도체 메모리 DRAM이야기 4편 (0) | 2024.08.13 |

| 반도체 메모리 DRAM이야기 2편 (0) | 2024.08.11 |

| 반도체 메모리 DRAM이야기 1편 (1) | 2024.08.11 |

| TSMC 2024 기술동향과 로드맵소개,패키징포함 (1) | 2024.08.02 |