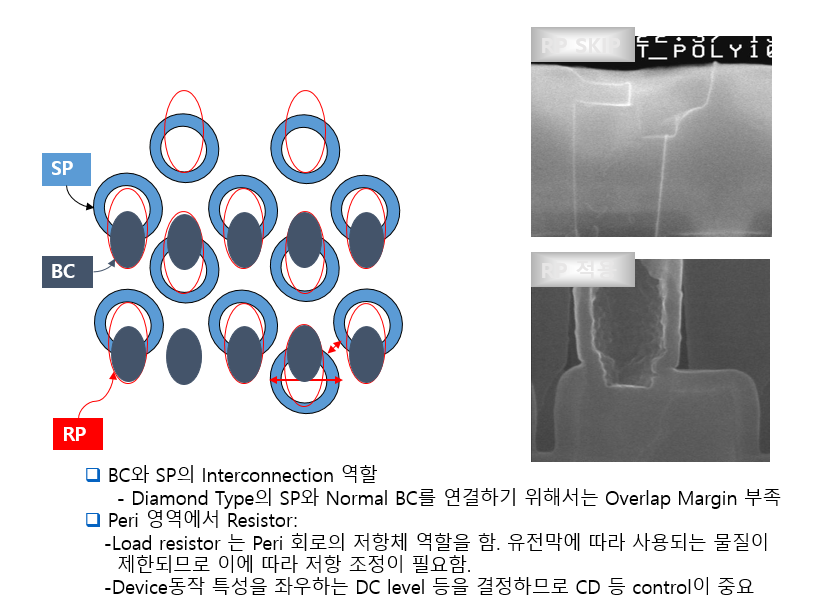

BC (Buried Contact)의 역할 : BC는 COB (Capacitor On Bit-line) 구조에서 cell transistor와 storage node를

연결하는 통로를 말한다. DRAM 공정에서 buried contact는 중요한 역할을 합니다. 주로 n+ 영역과 폴리실리콘 영역을 연결하는 데 사용됩니다. 이를 통해 전기적 연결을 효율적으로 만들고, 소자의 크기를 줄이면서도 성능을 유지할 수 있습니다. 또한, buried contact는 RC time delay를 줄이는 데도 기여합니다. 이는 신호 전달 속도를 높여 DRAM의 성능을 향상시키는 데 중요한 요소입니다.

BC 상세 공정(Photo)은 PR Flow 공정 필요하다(e-BC Scheme의 경우)

- AFI CD @ 105 → AFI CD @90

- M/A 관리 필요 : M/A 심하게 발생할 경우 BC Etch 시에 BL을 Touch로 Shoulder Margin 감소

RP(Resistor Poly)의 역할

Resistor Poly는 주로 트랜지스터 게이트의 역할을 하거나, 특정 전기적 특성을 제어하기 위해 사용됩니다. DRAM의 경우, 저항 폴리실리콘 층(RP)은 주로 다음과 같은 역할을 할 수 있습니다:

- 저항 역할: 특정 회로에서 전류의 흐름을 조절하는 저항 요소로 작용합니다. 이 저항은 데이터 저장 셀에서 전압을 안정화하고, 과도한 전류로 인한 손상을 방지합니다.

- 전기적 연결: RP는 종종 트랜지스터의 게이트로 사용되어, 전기적 신호를 제어하고 데이터 저장 셀의 동작을 결정합니다.

- 기판 보호: RP는 기판과 다른 도핑된 영역을 물리적으로 분리하는 역할도 할 수 있습니다. 이로 인해 전기적 간섭을 줄이고, 셀의 신뢰성을 높이는 데 기여합니다.

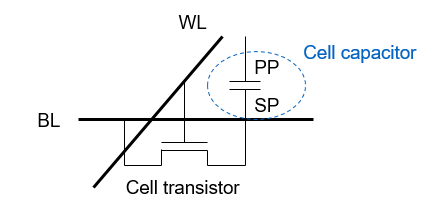

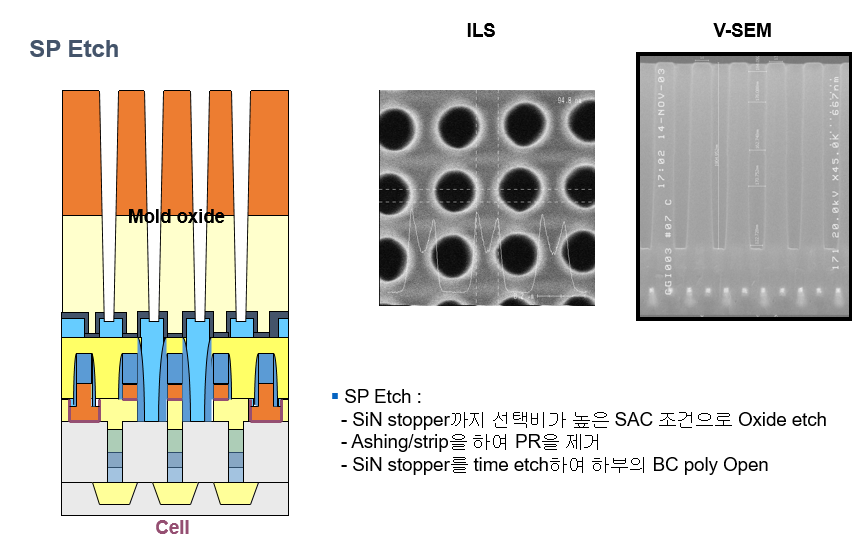

SP(Storage Poly)의 역할 : SP는 cell capacitor의 storage node 역할을 하며 cell transistor 및 cell contact을 통해 들어온 data “0” 혹은 “1”을 저장하는 역할을 한다. Cell capacitor는 SP와 PP (Plate poly) 및 이 사이에 형성된 얇은 유전막 (thin dielectric layer)으로 이루어진다.

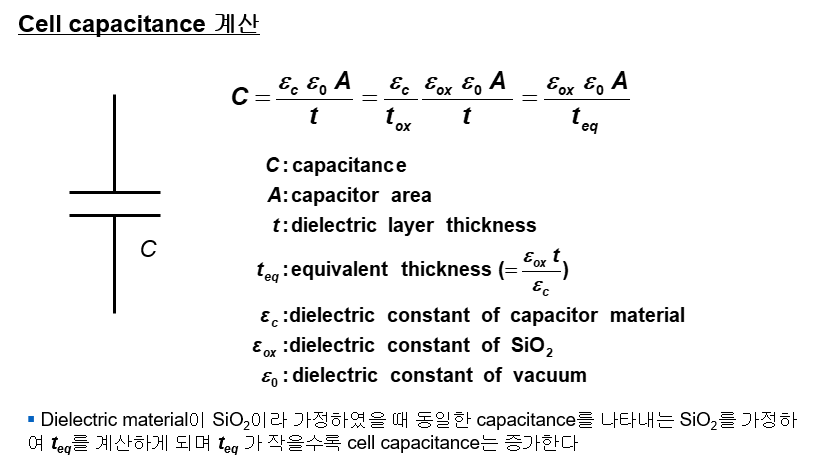

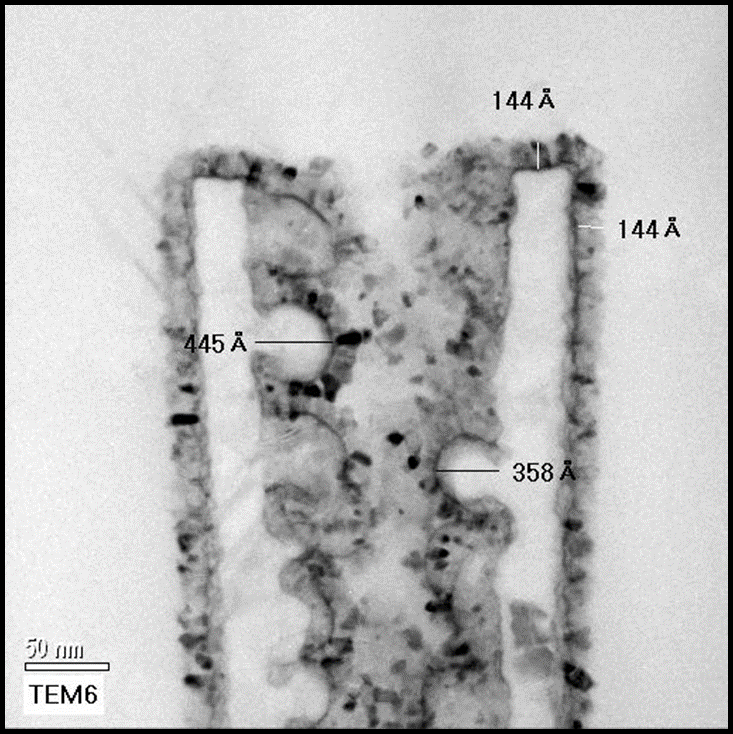

Cell Capacitor의 계산

셀 커패시터의 용량 CC는 다음과 같은 공식을 통해 계산할 수 있습니다:

TEM의 본 DRAM Capacitor모습

'반도체' 카테고리의 다른 글

| AI 공급망 분석 AI supply chain 서플라이체인 (0) | 2024.09.18 |

|---|---|

| AI칩 nvidia TSMC의 CoWoS 구조 (3) | 2024.08.23 |

| 반도체 메모리 DRAM이야기 3편 (0) | 2024.08.12 |

| 반도체 메모리 DRAM이야기 2편 (0) | 2024.08.11 |

| 반도체 메모리 DRAM이야기 1편 (1) | 2024.08.11 |