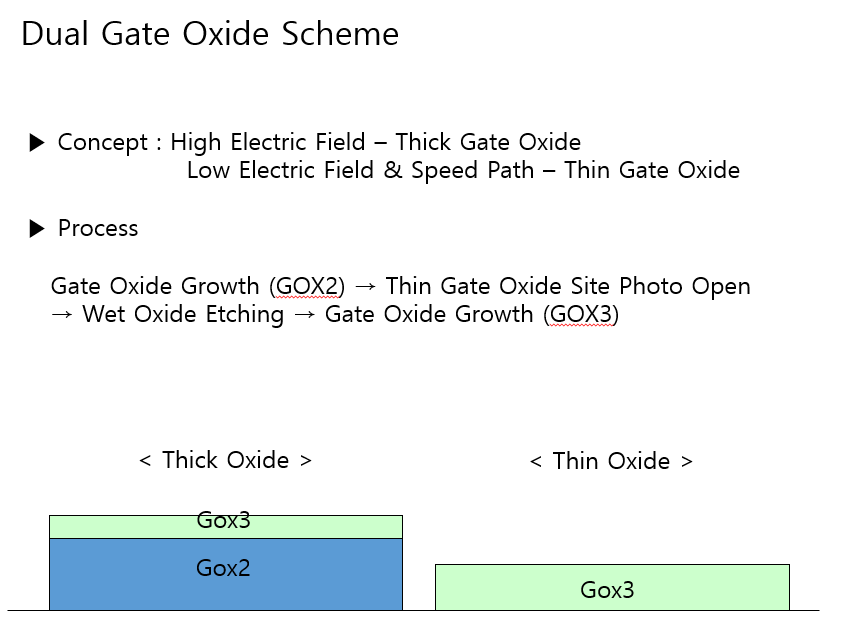

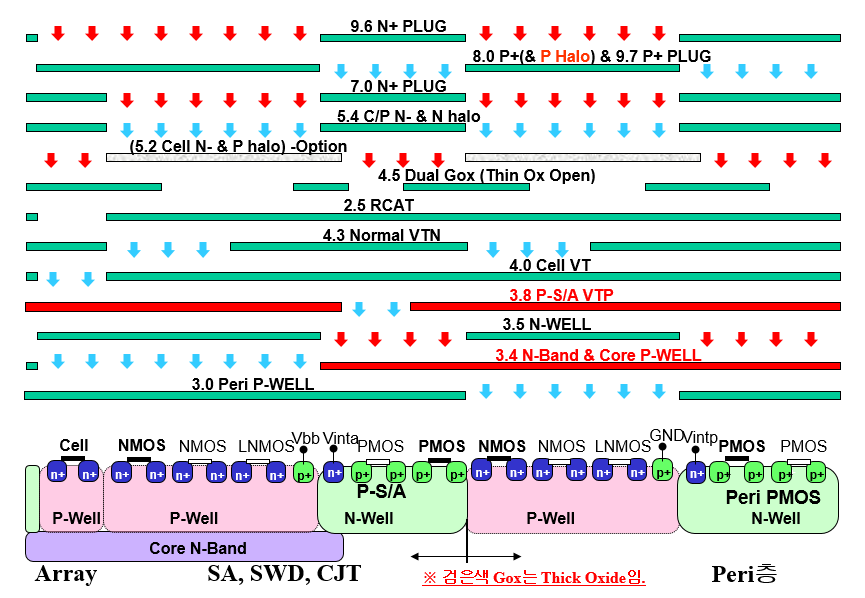

DRAM에서 Dual Gate Oxide Scheme은 반도체 소자의 게이트 산화막 두께를 두 가지로 나누어 설계하는 방법을 말합니다. 이 방식은 DRAM 소자의 성능을 최적화하고, 고속 동작과 신뢰성을 동시에 확보하기 위해 사용됩니다.

Dual Gate Oxide Scheme의 개념

- 두 가지 다른 두께의 게이트 산화막 사용:

- DRAM 소자의 트랜지스터에서 게이트 산화막의 두께를 두 가지로 구분하여 설계합니다. 일반적으로 얇은 산화막과 두꺼운 산화막을 사용하게 됩니다.

- 얇은 산화막:

- 얇은 산화막은 **접속 트랜지스터(access transistor)**와 같이 고속 동작이 요구되는 소자에 사용됩니다. 얇은 산화막은 게이트 전압에 더 민감하게 반응하여 전자 이동 속도가 빨라지고, 이로 인해 전류 구동 능력이 향상되며, 고속 동작이 가능해집니다.

- 그러나 얇은 산화막은 **누설 전류(leakage current)**가 증가할 수 있고, 열화(degradation)가 더 쉽게 발생할 수 있어, 장기적인 신뢰성 문제가 발생할 수 있습니다.

- 두꺼운 산화막:

- 두꺼운 산화막은 **데이터 저장 트랜지스터(storage transistor)**와 같이 데이터의 안정적 저장이 중요한 소자에 사용됩니다. 두꺼운 산화막은 전자 이동 속도가 상대적으로 느리지만, 누설 전류가 감소하여 데이터가 더 안정적으로 저장될 수 있습니다. 또한, 두꺼운 산화막은 소자의 신뢰성을 높여, 장기간 동작에서도 성능 저하가 적습니다.

Dual Gate Oxide Scheme의 장점

- 성능 최적화:

- 고속 동작이 필요한 영역에는 얇은 산화막을, 안정성이 중요한 영역에는 두꺼운 산화막을 사용함으로써 성능과 신뢰성을 모두 확보할 수 있습니다.

- 전력 소모 감소:

- 두꺼운 산화막을 사용함으로써 누설 전류를 줄일 수 있어 전력 소모를 줄이는 데 기여할 수 있습니다.

- 소자 신뢰성 향상:

- 각 소자에 맞는 최적의 산화막 두께를 사용하여 소자의 수명과 안정성을 향상시킬 수 있습니다.

Dual Gate Oxide Scheme의 적용 및 고려 사항

이 방식은 DRAM뿐만 아니라, 다른 고성능 반도체 소자에서도 적용될 수 있습니다. 그러나 제조 공정이 복잡해지고 비용이 증가할 수 있으므로, 이러한 요소를 고려하여 설계 및 공정 최적화가 필요합니다. Dual Gate Oxide Scheme은 특히 고속 동작이 필요한 메모리 소자나 신뢰성이 중요한 반도체 소자에서 중요한 기술로 자리잡고 있습니다.

여기서 RCAT이라는 공정이 나옵니다.

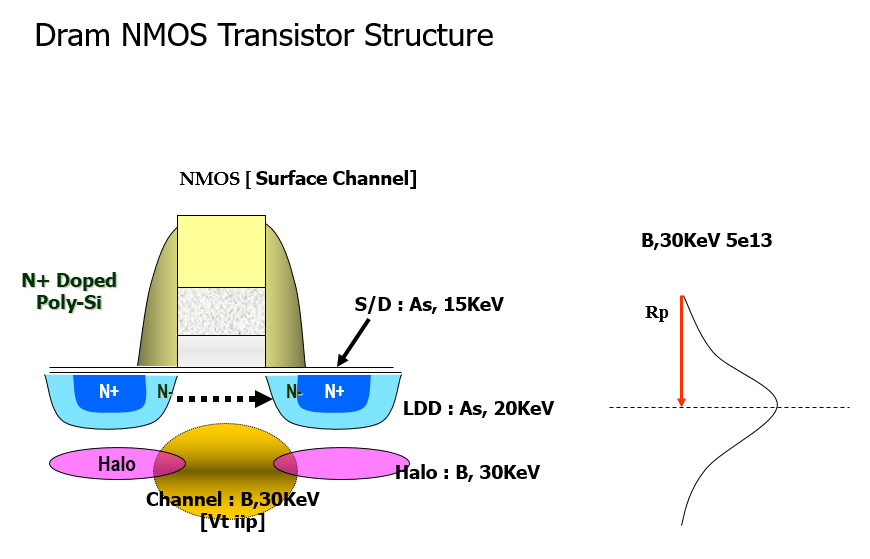

RCAT(Recessed Channel Array Transistor)

RCAT는 트랜지스터의 채널이 반도체 기판 속으로 파묻힌 형태를 가지며, 이로 인해 더 안정적인 문턱 전압을 유지하고, 누설 전류를 줄일 수 있습니다. 그리고 RCAT 구조는 채널 길이를 효과적으로 제어할 수 있어, 문턱 전압의 변동성을 줄이고 소자의 균일성을 높입니다. 문턱 전압의 변동은 DRAM의 성능에 큰 영향을 미치며, 특히 데이터 유지 시간(retention time)과 소자 신뢰성에 부정적인 영향을 미칠 수 있습니다. RCAT 구조는 채널을 반도체 기판에 깊이 파고들어가게 하여, 문턱 전압을 안정적으로 유지하면서도 소형화를 가능하게 합니다.

RCAT 구조의 특징

- 채널이 기판에 파묻힌 구조: RCAT는 트랜지스터의 채널이 반도체 기판 속으로 파묻힌 형태를 가지며, 이로 인해 더 안정적인 문턱 전압을 유지하고, 누설 전류를 줄일 수 있습니다.

- 효율적인 공간 활용: 기존의 평면형 구조보다 더 작은 면적에서 동일한 기능을 수행할 수 있어, 더 높은 집적도를 구현할 수 있습니다.

- 문턱 전압 변동성 감소: RCAT 구조는 채널 길이를 효과적으로 제어할 수 있어, 문턱 전압의 변동성을 줄이고 소자의 균일성을 높입니다.

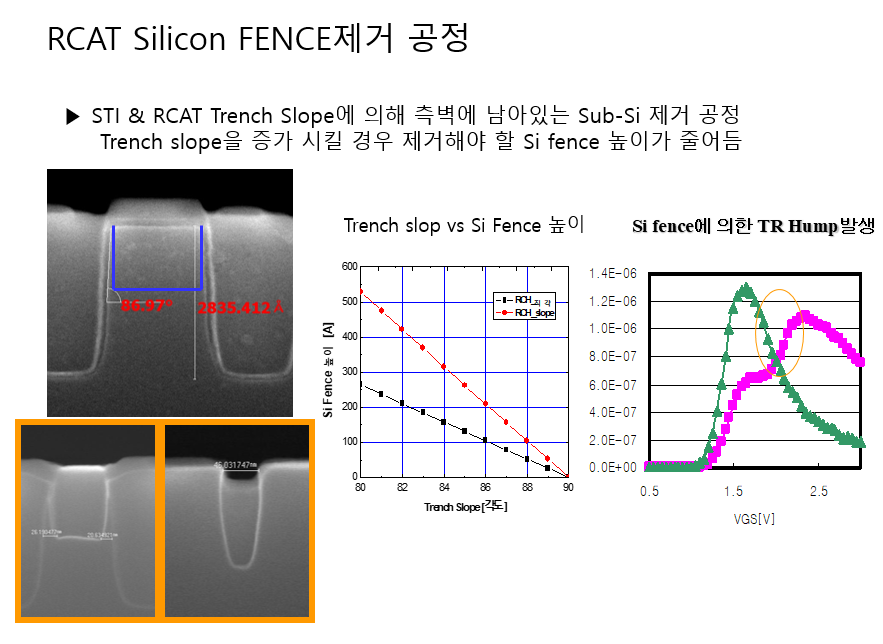

RCAT (Recessed Channel Array Transistor) 구조에서 **Si FENCE(실리콘 펜스)**는 제조 과정에서 트랜지스터의 성능을 저하시키는 원인이 될 수 있는 불필요한 실리콘 구조물입니다. Si FENCE 제거 공정은 이러한 불필요한 구조물을 제거하여 RCAT의 성능을 최적화하는 데 중요한 역할을 합니다. RCAT 공정 중 실리콘 식각 단계에서, 특정 영역에 **잔여 실리콘(Si FENCE)**이 남을 수 있습니다. 이러한 실리콘 잔여물은 트랜지스터의 채널 영역 주변에 형성되며, 의도하지 않은 누설 경로를 제공하거나, 채널 전류를 방해하는 등 소자의 성능에 악영향을 미칠 수 있습니다.

RCAT의 Si FENCE 제거 공정은 소자의 성능과 신뢰성을 높이기 위해 중요한 단계입니다. 이 공정을 통해 채널 전류를 최적화하고, 불필요한 누설 전류를 줄이며, 소자의 장기적 신뢰성을 보장할 수 있습니다. 이를 위해 정밀한 선택적 식각과 세정 공정이 필요하며, 이후 철저한 검사를 통해 최종 소자의 품질을 보증합니다.

RCAT 구조는 채널이 반도체 기판 속으로 깊이 파고들어간 형태이기 때문에, 전통적인 평면형 트랜지스터에 비해 기판과 채널 간의 전기적 상호작용이 더욱 복잡해집니다. 이로 인해 Body Effect가 더 두드러지게 나타날 수 있으며, 이를 정확히 모델링하는 것이 중요합니다.

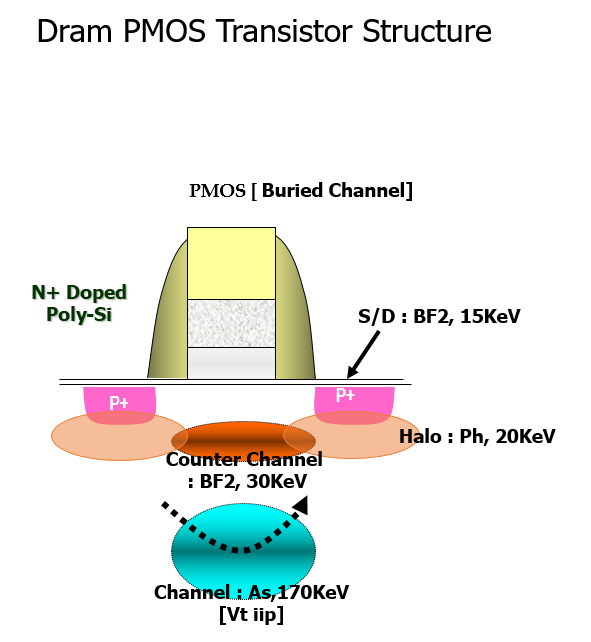

트랜지스터 타입의 종류

'반도체' 카테고리의 다른 글

| 반도체 메모리 DRAM이야기 4편 (0) | 2024.08.13 |

|---|---|

| 반도체 메모리 DRAM이야기 3편 (0) | 2024.08.12 |

| 반도체 메모리 DRAM이야기 1편 (1) | 2024.08.11 |

| TSMC 2024 기술동향과 로드맵소개,패키징포함 (1) | 2024.08.02 |

| 반도체 EUV미세공정에 따른 CD측정 도전과 Hitachi사GT2000의 혁신 (0) | 2024.08.01 |